|

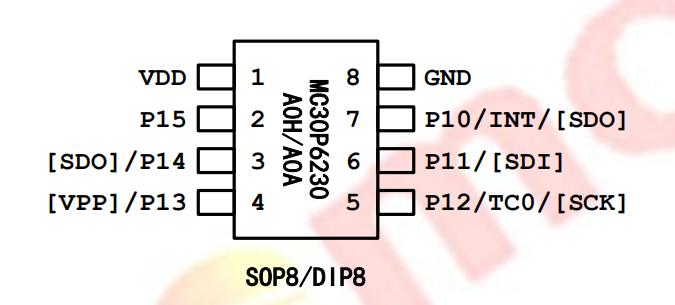

晟矽微MC30P6230

◆ 8位CPU内核 ▲ 精简指令集,5级深度硬件堆栈 ▲ CPU单时钟,仅在系统高频时钟下工作 ▲ 高频时钟下FCPU固定为2T ◆ 程序存储器 ▲ 1K×14位OTP型程序存储器(烧录1次) ▲ 0.5K×14位OTP型程序存储器(烧录2次) ◆ 数据存储器 ▲ 50字节SRAM通用数据存储器,支持直接寻址、间接寻址等多种寻址方式 ◆ 1组共6个I/O ▲ P1(P10~P15) ▲ P13为开漏输出,可复用为编程高压VPP输入;其余端口可选开漏或推挽输出 ▲ 所有端口均内置上拉电阻,P10~P12内置下拉电阻,均可单独使能/禁用 ◆ 时钟系统 ▲ 内置高频RC振荡器(8MHz/4MHz/2MHz/1MHz/455KHz),可用作系统高频时钟源 ▲ 内置低频RC振荡器(32KHz),可用作系统低频时钟源 ◆ 2种系统工作模式 ▲ 运行模式:CPU在高频时钟下运行 ▲ 休眠模式:CPU停止运行,高频时钟源停止工作 ◆ 内部自振式看门狗计数器(WDT) ▲ 溢出时间可配置:4.5ms/18ms/72ms/288ms(无预分频) ▲ 工作模式可配置:开启WDT、关闭WDT;也可软件控制开启或关闭 ▲ 与定时器T0共用3位预分频器 ◆ 定时器 ▲ 8位定时器T0,可实现外部计数功能,与WDT共用3位预分频器 ◆ 中断 ▲ 外部中断(INT):INT可选两种触发方式 ▲ 定时器中断(T0):溢出产生中断 ▲ 键盘中断:6路端口共用1个中断源,并可分别使能或屏蔽 ◆ 低电压复位LVR:2.0V/2.7V/3.0V/3.6V,±15% ◆ 工作电压 ▲ VLVR27 ~ 5.5V @ Fcpu = 4MHz(FHIRC=8MHz) ▲ VLVR20 ~ 5.5V @ Fcpu = 2MHz(FHIRC=4MHz) ▲ VLVR20 ~ 5.5V @ Fcpu = 227.5KHz(FHIRC=455KHz) ◆ 封装形式:SOP8/DIP8/SOT23-6 上一篇晟矽微MC30P7050下一篇晟矽微MC30P6080 |

|

|

|

|