4K(FLASH)+E方 运放 MC F7062

1 产品概要

1.1 产品特性

8 位 CPU 内核

精简指令集,8 级深度硬件堆栈 CPU 为双时钟,可在系统高/低频时钟之间切换

系统高频时钟下 FCPU 可配置为 FHOSC 的 2/4/8/16/32/64 分频

系统低频时钟下 FCPU 固定为 FLOSC 的 2 分频

程序存储器 4K×16 位 FLASH 型程序存储器,可通过间接寻址读取程序存储器内容 支持在板不带电烧录编程

数据存储器 256 字节 SRAM 型通用数据存储器,支持直接寻址、间接寻址等多种寻址方式

256 字节 EEPROM 型数据存储器,支持单独烧录和软件读写,擦写次数至少 10 万次

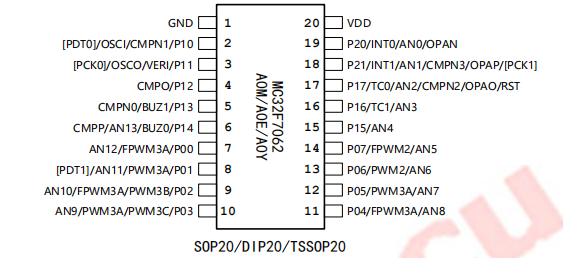

3 组共 18 个 I/O P0(P00~P07),P1(P10~P17),P2(P20~P21)

所有端口均支持施密特输入,均支持推挽输出

P17 可复用为外部复位 RST 输入,P10/P11 可复用为外部时钟振荡器输入/输出

所有端口均内置上拉和下拉电阻,均可单独使能

P20/P21 可复用为外部中断输入,支持外部中断唤醒功能

P1 所有端口均支持键盘中断唤醒功能,并可单独使能

系统时钟源 内置高频 RC 振荡器(32MHz/2MHz),可用作系统高频时钟源,支持软件微调

支持外接高频晶体振荡器(455KHz/4MHz~16MHz),可用作系统高频时钟源

内置低频 RC 振荡器(32KHz),可用作系统低频时钟源

支持外接低频晶体振荡器(32768Hz),可用作系统低频时钟源

系统工作模式 高速模式:CPU 在高频时钟下运行,低频时钟源工作

低速模式:CPU 在低频时钟下运行,高频时钟源可选停止或工作

HOLD 模式(低功耗模式):CPU 暂停,高频时钟源停止,低频时钟源工作

休眠模式(低功耗模式):CPU 暂停,高/低频时钟源均停止

内部自振式看门狗计数器(WDT) 溢出时间可配置:16ms/64ms/256ms/1024ms

工作模式可配置:始终开启、始终关闭、低功耗模式下关闭

4 个定时器 8 位定时器 T0,可实现外部计数和 BUZ 功能

16 位定时器 T1,可实现外部计数、BUZ 和内/外部信号输入捕捉功能

8 位定时器 T2,可实现 1 对 8+3 模式的带死区互补 PWM

8 位定时器 T3,可实现 3 路共周期独立占空比的 PWM(其中 1 路可扩展为 1 对 8+3 模式 的带死区互补 PWM,且可从 3 组端口输出并支持输出保护功能)

1 个 12 位高精度 SAR 型 ADC

14 路外部通道:AN0~AN13;2 路内部通道:GND、VDD/4

参考电压可选:VDD、内部参考电压 VIR(2V/3V/4V)、外部参考电压 VER(VERI 输入)

ADC 时钟:FCPU 的 2/4/8/16 分频 支持零点校准

1 个模拟比较器 CMP 输入共模 0 ~(VDD-1.4V),支持失调电压自消除调校(调校精度±2mV),输出无回滞且 支持去抖处理

正端输入可选择外部输入电压、或 VDD 内部分压电压

负端输入可选择外部输入电压

输出端电平可选择上升沿或下降沿触发中断,可从端口输出且支持输出取反

1 个运算放大器 OPA 输入共模 0 ~(VDD-1.4V),开环放大倍数 60dB

中断 外部中断(INT0~INT1),键盘中断(P10~P17)

定时器中断(T0~T3),T1 捕捉中断 ADC 中断,CMP 中断,LVD 中断

低电压检测 LVD:2.0V/2.2V/2.4V/2.6V/2.8V/3.2V/3.6V/4.0V

低电压复位 LVR:2.0V/2.4V/2.7V/3.2V

工作电压(@HIRC)

VLVR32 ~ 5.5V @ Fcpu = 0~16MHz VLVR24 ~ 5.5V @ Fcpu = 0~8MHz

VLVR20 ~ 5.5V @ Fcpu = 0~4MHz

封装形式:SOP20/DIP20/TSSOP20/SOP16/DIP16/SOP14/SOP8/DIP8

推荐

-

-

QQ空间

-

新浪微博

-

人人网

-

豆瓣